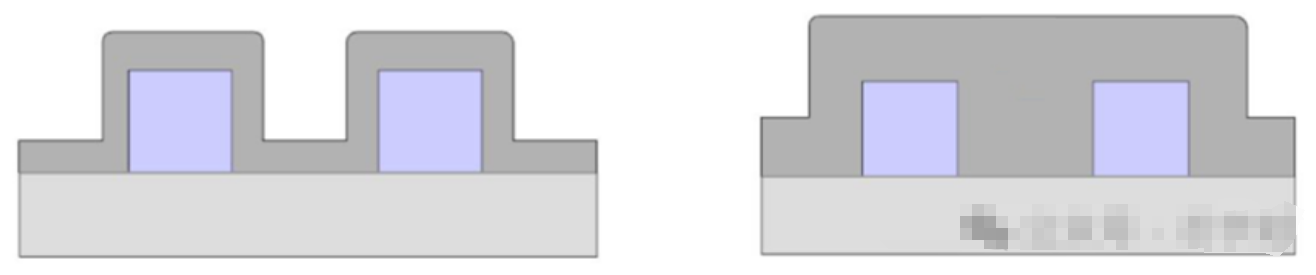

薄膜的保角性,又称保形性,指的是薄膜淀积台阶覆盖能力和空隙填充能力,以及保留原始形状的能力。因此,保角性不能和台阶覆盖性划等号,保角性的概念包含了台阶覆盖的概念。

薄膜保角性,要求所有图形上(表面、底面和侧壁)淀积的薄膜厚度相同,也称共性覆盖。而台阶覆盖性,不要求沿着台阶所有界面的膜层厚度是均匀的,只要能覆盖下层。因此,薄膜保角性比台阶覆盖性要求更高。那么如果做到好的保角性呢?要求淀积物在台阶表面吸附后迅速迁移,才能使薄膜厚度均匀。这样就有必要介绍薄膜的沉积方式。

图 保角性和台阶覆盖性的比较

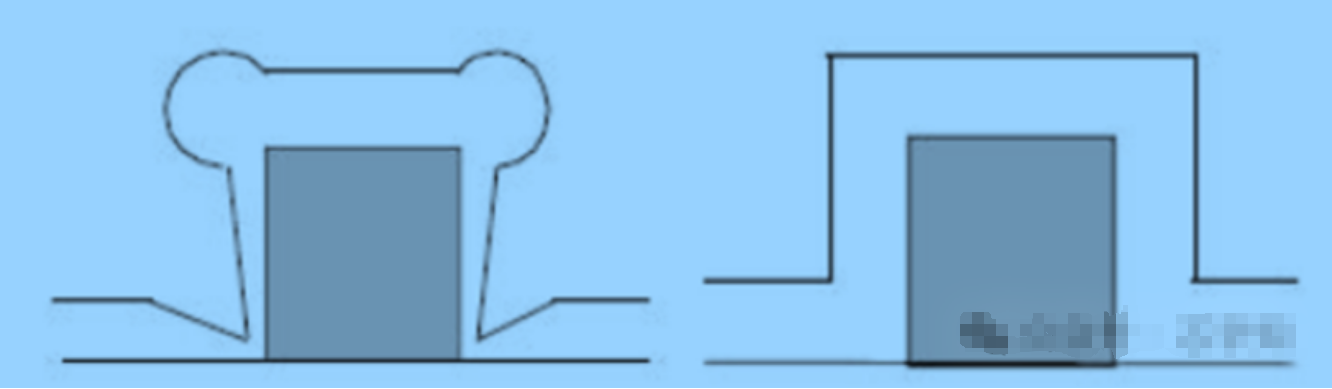

物理气相沉积(PVD,Physical Vapor Deposition),一般针对淀积金属薄膜。是在真空条件下,金属源通过物理驱动传输到衬底上,主要的方法包括蒸发和溅射。这里不再介绍蒸发和溅射的细分类和具体原理过程。PVD淀积薄膜在不平整的表面时,在表面淀积的速率明显高于侧壁,且侧壁越靠下,淀积速率越低,造成台阶顶部的突悬。高深宽比的台阶,基本不提保角性,甚至无法做到良好的台阶覆盖,侧壁靠下部分无法淀积薄膜。这也是TGV和TSV技术,通孔填铜的技术难点和具有挑战性的点。那么对比蒸发和溅射,哪种台阶覆盖更好呢?一般而言,认为溅射更好,尤其是射频磁控溅射,通过衬底加热和对衬底施加射频都可以提高台阶覆盖性。

图 台阶悬突和台阶保角

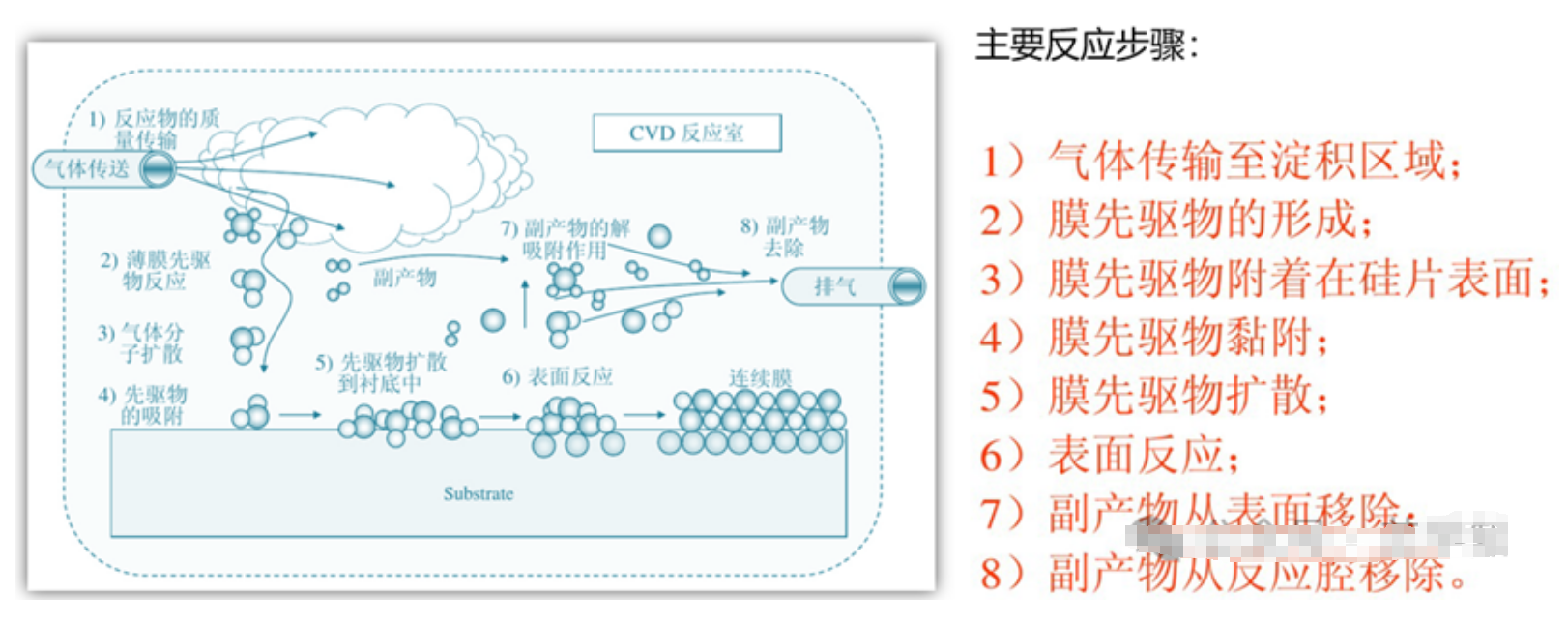

化学气相沉积(CVD,Chemical Vapor Deposition)是半导体工业中应用最为广泛的材料淀积技术,包括大部分的的介质薄膜和少量的金属薄膜。从原理上说,两种或两种以上的气态或液态原材料导入到一个反应室内,通过吸附、化学反应和排出副产物,形成目标膜层在衬底淀积。由于CVD是直接在图形上生成目标物,因此它的保角性是值得探索和研究的。CVD参数的可调范围是很宽:反应室内的压力、晶片的温度、气体的流动速率、气体通过晶片的路程、气体的化学成份、一种气体相对于另一种气体的比率等,合适的淀积参数确定,是形成保角性的必要条件。

图 CVD沉积原理图示和反应步骤

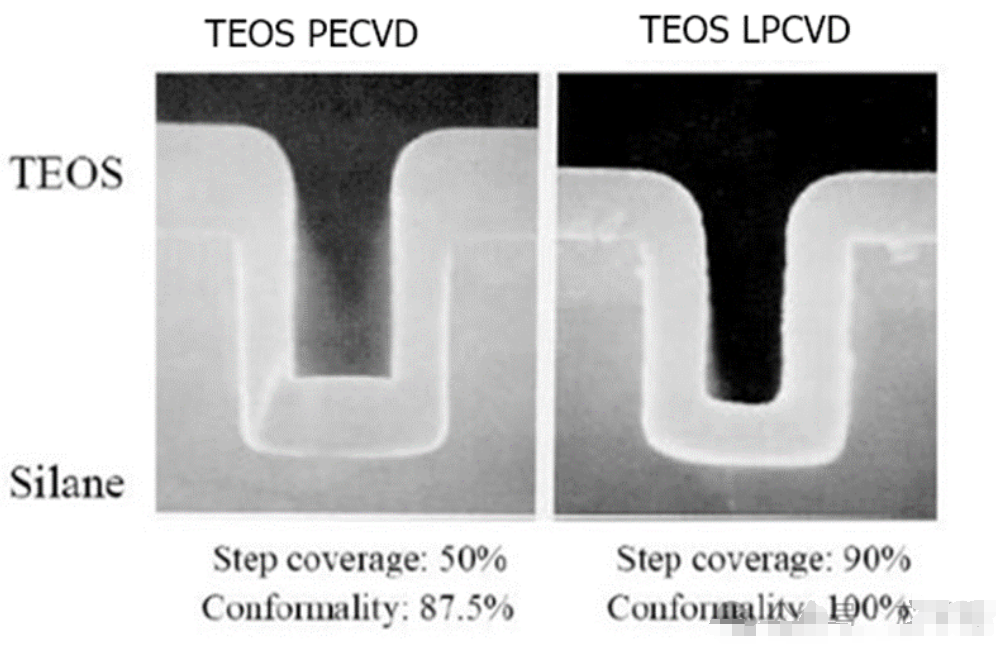

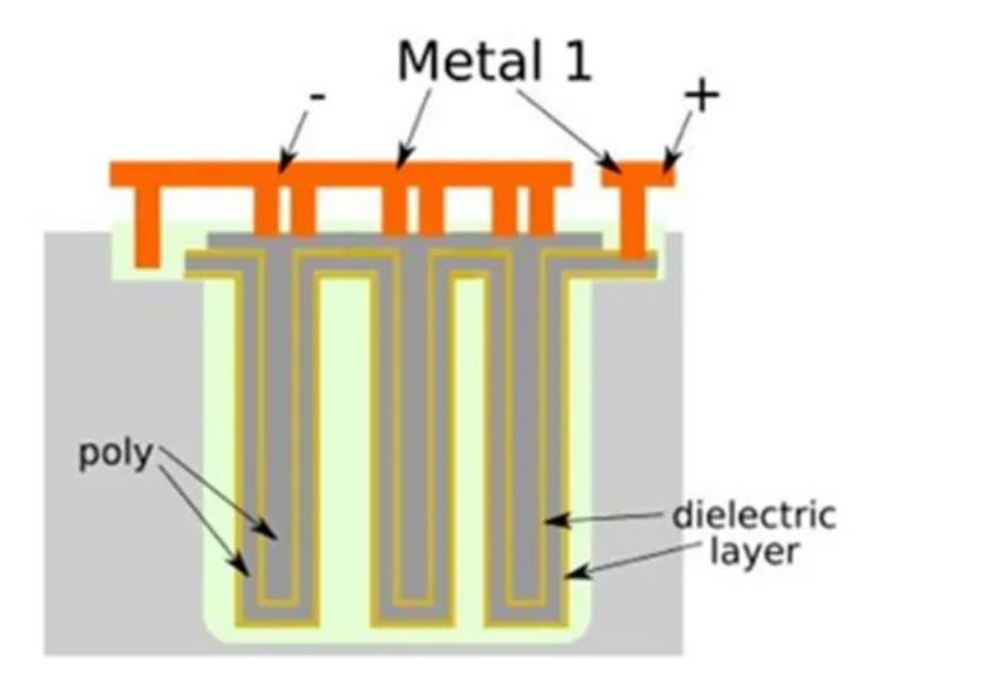

CVD技术常常通过反应类型或者压力来分类,包括低压CVD(LPCVD),常压CVD(APCVD),亚常压CVD(SACVD),超高真空CVD(UHCVD),等离子体增强CVD(PECVD),高密度等离子体CVD(HDPCVD)和快热CVD(RTCVD)。一般情况,搭配液态源的LPCVD和PECVD有可能实现较好的薄膜保角性。正硅酸乙脂(TEOS)为无色透明液体,在700 ℃以上,低压掺氧条件下分解可产生二氧化硅和有机物,其中氧对TEOS热分解起到催化作用,其介质层膜厚均匀、保角性好且具有良好的介电性能。在硅电容中,即采用LPCVD在深沟槽内沉积多晶硅淀积极板层。

图 TEOS的两种CVD台阶覆盖性和保角性的比较

另外介绍一种保角性近乎100%的技术,原子层沉积ALD,这也是CVD的一种。ALD是一层一层的生长工艺,每一周期有自约束,因此对于超薄层生长的控制要好得多。在衬底绝缘层氧化物上,对保角性要求高且薄膜厚度低的场景非常适用。在硅电容中,深沟槽中的绝缘层即可采用ALD保证其厚度均匀性好。

图 深沟槽硅电容示意图

尽管CVD比PVD有更好的台阶覆盖特性,但目前通孔填铜的种子层和钽氮扩散层薄膜都是通过PVD来淀积的,CVD实际应用大部分在介质膜和绝缘膜,实际的工艺选择还是需要根据芯片的设计要求,并不是说所有的膜层都要求100%保角性。

声明:转载此文是出于传递更多信息之目的,若有来源标注措误或侵犯了您的合法权益,请与我们联系,我们将及时更正、删除,谢谢。

分享